IT采購網(wǎng)2月17日消息,持續(xù)提升芯片性能的關(guān)鍵在于不斷縮小晶體管尺寸,而半導體行業(yè)對此的探索從未止步。然而,隨著技術(shù)的發(fā)展,光刻技術(shù)也面臨著一些挑戰(zhàn)。

ASML首席技術(shù)官Martin van den Brink曾在2022年9月表示,經(jīng)過數(shù)十年的創(chuàng)新,High-NAEUV可能已接近其技術(shù)極限。然而,令人欣喜的是,在經(jīng)過一年多的深入探索后,ASML在《2023年度報告》中提出了一個全新的概念——Hyper-NAEUV,預計將在2030年左右問世。

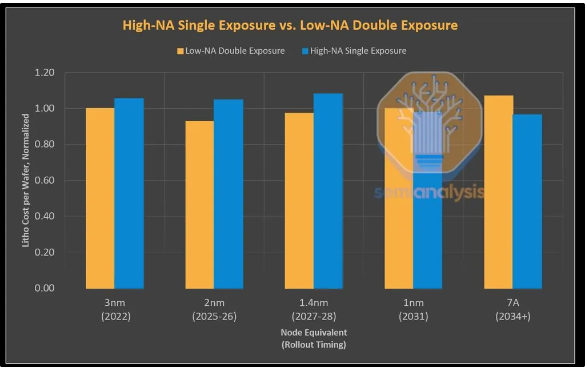

據(jù)IT采購網(wǎng)了解,Brink在報告中指出,Hyper-NA的數(shù)值孔徑(NA)高于0.7,這將為半導體行業(yè)帶來新的機遇。與High-NAEUV相比,Hyper-NA在成本上更具優(yōu)勢,同時它還能為DRAM等領(lǐng)域帶來新的可能性。對于ASML而言,Hyper-NA有望推動其整體EUV能力的提升,從而改善成本和交付周期。

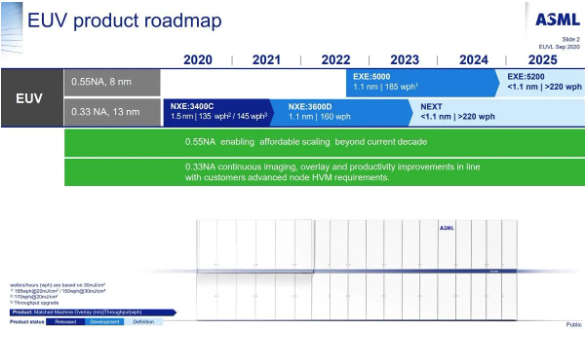

目前,ASML的Low-NAEUV光刻工具已經(jīng)能夠支持4nm/5nm工藝芯片的生產(chǎn)。然而,隨著工藝的不斷進步,3nm及以下的工藝對光刻技術(shù)的要求也在不斷提高。盡管High-NAEUV在一定程度上能夠滿足這些需求,但金屬間距在1nm之后的進一步縮小仍然是一個巨大的挑戰(zhàn)。

為了應對這一挑戰(zhàn),ASML正在積極研究Hyper-NA技術(shù)的可行性。雖然目前還沒有做出最終決定,但公司已經(jīng)在探索開發(fā)這種更先進的光刻工具。然而,提高投影光學器件的數(shù)值孔徑不僅需要巨大的投資,還需要重新設計光刻工具和開發(fā)新的組件,這無疑將增加成本的壓力。

根據(jù)微電子研究中心(IMEC)的路線圖,到2030年左右,半導體工藝有望推進到A7 0.7nm。而在這個過程中,Hyper-NAEUV技術(shù)有望發(fā)揮關(guān)鍵作用。當然,隨著技術(shù)的不斷進步和市場需求的不斷變化,半導體行業(yè)還需要持續(xù)探索和創(chuàng)新,以應對未來的挑戰(zhàn)和機遇。